バックエンド設計時では、回路の積分電荷量を調べることでHTフリー性を保証します。

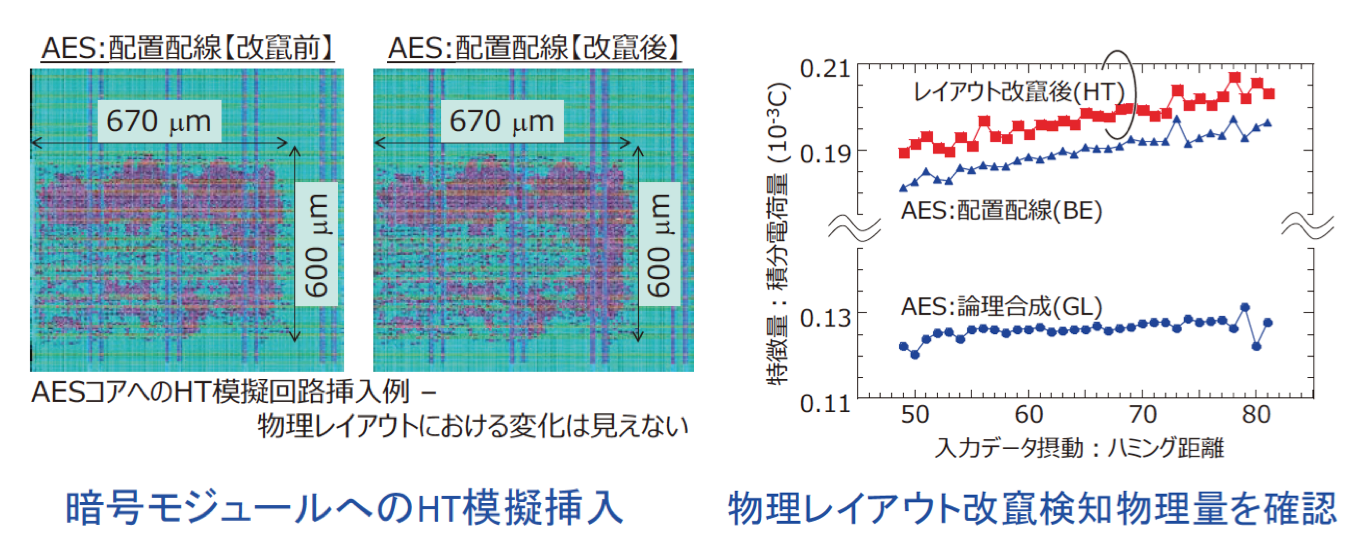

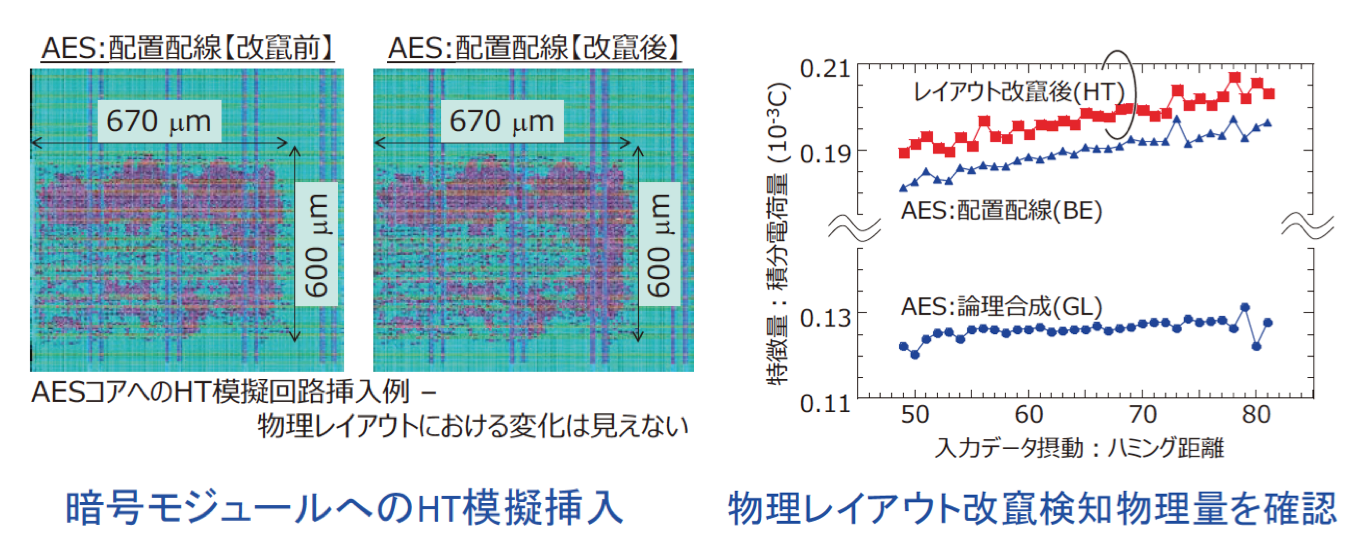

たとえば、少し大きなコンデンサ等の挿入によって、回路の電気的な動きに変化を与えるHTがあります。しかし、暗号アルゴリズム(AES)を具現する集積回路に模擬的にそうしたHTを挿入し、改ざんされた回路と改ざん前の回路の物理レイアウトを比較しても、変化を認識することはできません。

ですが、各回路の電荷量を測定し、積分電荷量を比較すると、改ざん前と改ざん後では有意差が見られます。下図の右のグラフは、バックエンド設計データのシミュレーションにより、実際に製造される集積回路について物理レイアウトの改ざん前後で数値を比較したものです。

HTが挿入されても物理レイアウトレベルでは変化を確認できないが、積分電荷量を比較することで、改ざんされた回路が区別可能となる

このように積分電荷量から潜在的なHTを検出できることがわかったため、高速かつ高精度な電源消費電流シミュレーションによって回路の摂動的改変を検知する手法を構築しました。

LSI製造後に挿入されるHTへの対策は、これまで全く講じられていませんでした。

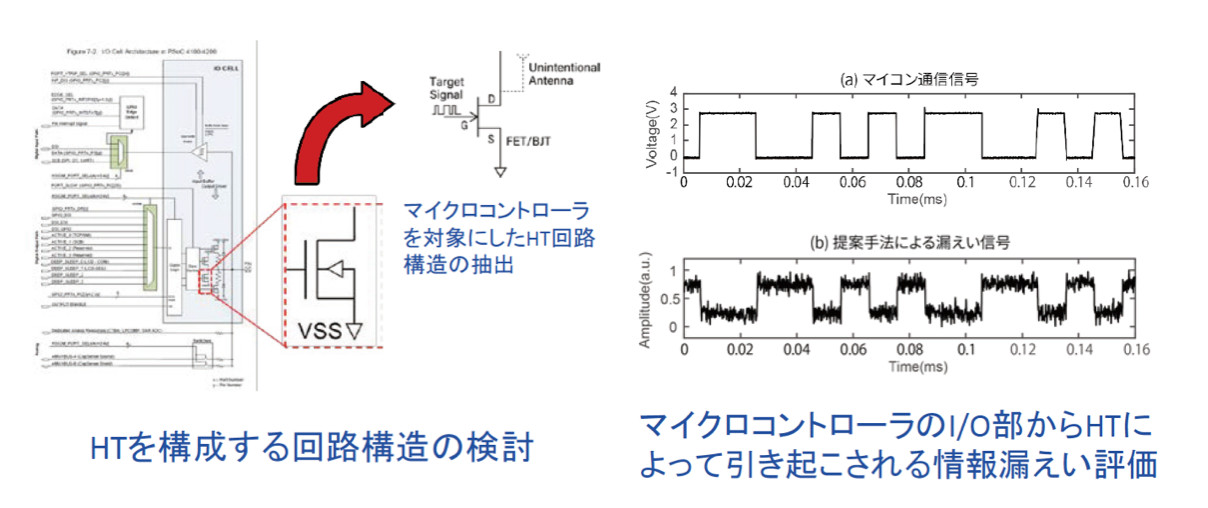

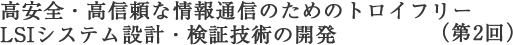

HTの基本機能は、情報漏洩、機能改変、サービス不能です。本研究では、各々を実現する回路構成を明らかにすることで、HTを実装しやすい基板や、潜在的にHTとして動く可能性がある素子およびそのレイアウトパターンを網羅的に抽出し、それらの知見をもとに、HT挿入が困難になる基板レベルでのデザインパターンの開発を目指しています。この部分は共同研究者の林優一先生(奈良先端科学技術大学院大学 教授)の専門領域です。

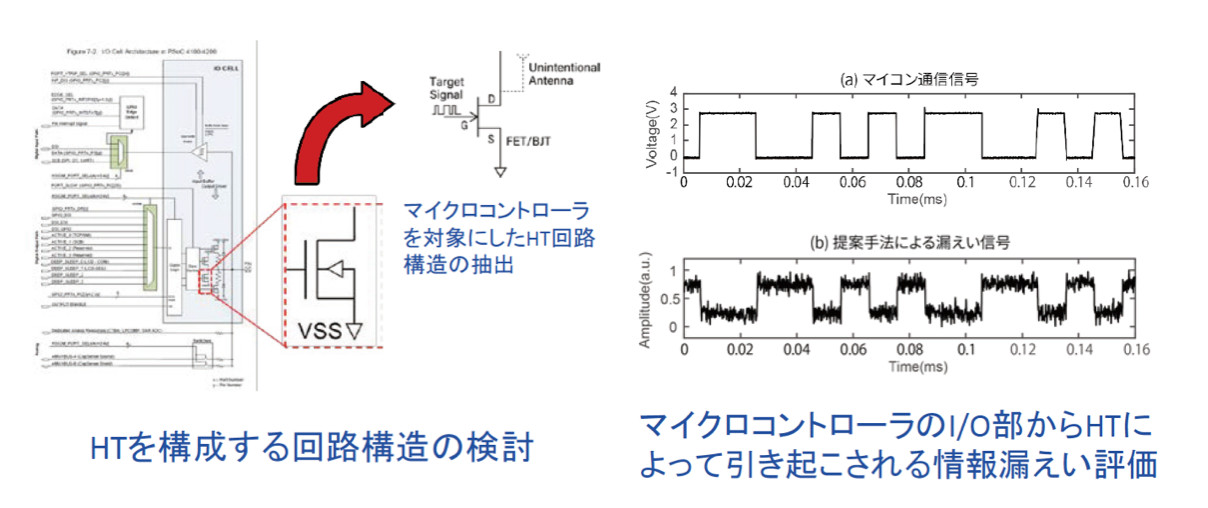

とくにセキュリティに重大な影響を及ぼす情報漏洩に着目し、漏洩を高精度に評価する計測法を開発するとともに、実際のシステムを対象に、その計測法を用いて情報漏洩が生じる可能性について評価実験を行いました。その結果、マイクロコントローラーにある回路構造が存在すると、その部分で情報が増幅され、電磁波とともに外部に漏洩することを突き止めました。現在は、このような構造を検出する技術の開発を進めています。

HTとなる回路構造の調査・評価。電磁界シミュレーションを駆使したHT検出技術の開発は、世界的に見ても先駆的な取り組み

HTが挿入されても物理レイアウトレベルでは変化を確認できないが、積分電荷量を比較することで、改ざんされた回路が区別可能となる

HTが挿入されても物理レイアウトレベルでは変化を確認できないが、積分電荷量を比較することで、改ざんされた回路が区別可能となる

HTとなる回路構造の調査・評価。電磁界シミュレーションを駆使したHT検出技術の開発は、世界的に見ても先駆的な取り組み

HTとなる回路構造の調査・評価。電磁界シミュレーションを駆使したHT検出技術の開発は、世界的に見ても先駆的な取り組み