それでは、計測したEMFPから真正性や経年劣化量を特定する手法について教えてください。

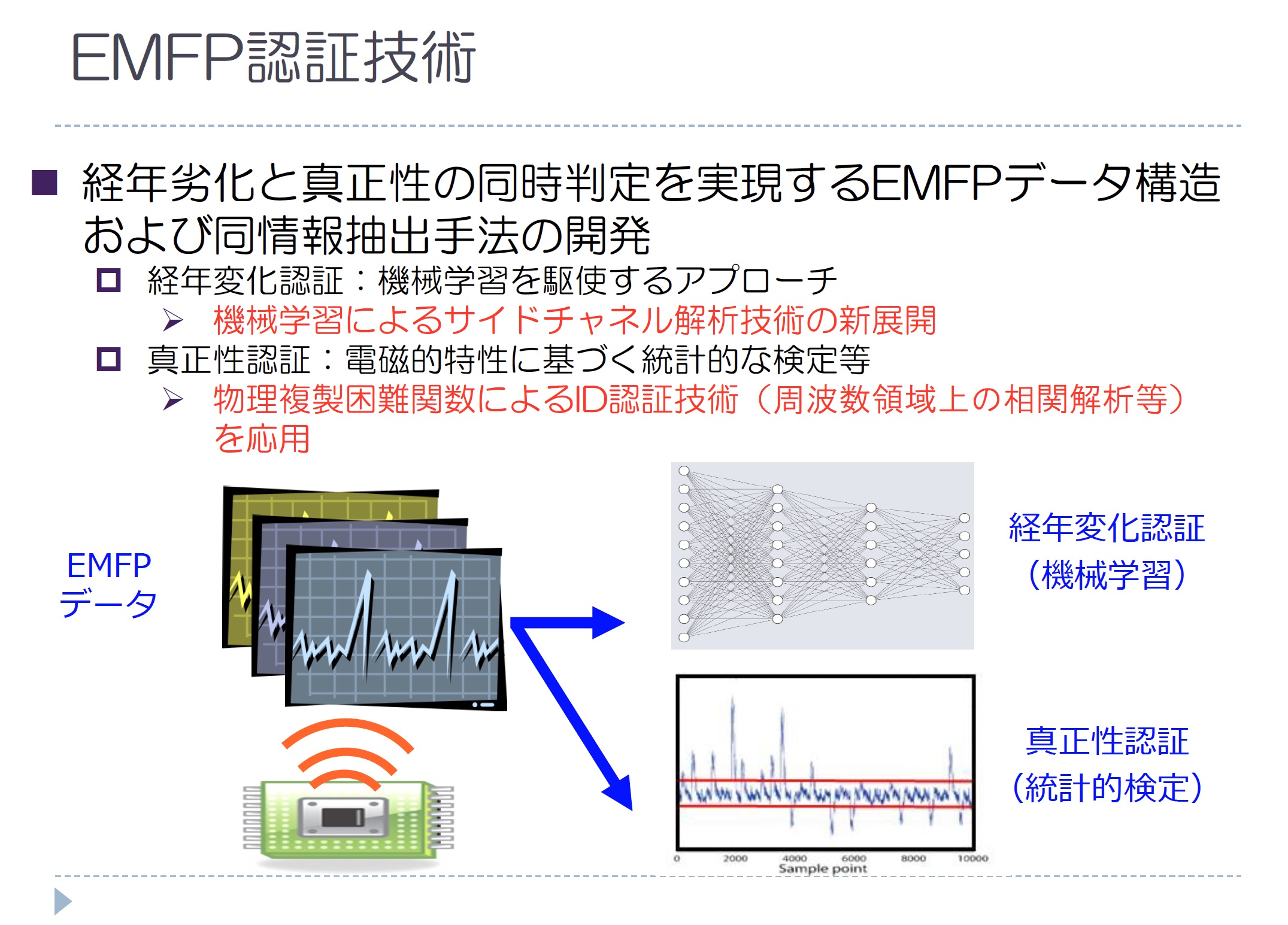

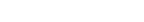

この課題には、東北大学の本間先生の研究チームが取り組んでいます。劣化が進むと、前回ご説明したように「ピーク時に高周波帯域の信号成分が減衰する」といった現象が確認されるほか、暗号回路の特徴的な波形にも変化が生じます。こうした多様なEMFPデータをニューラルネットワークに入力して学習させることで、「経年劣化推定モデル」と「真正性判定モデル」の構築を目指しています。

着目しているのは、暗号回路が処理を行う際に漏洩する電磁波情報、すなわちサイドチャネルです。セキュリティ分野では、これを解析して秘密鍵情報を取得する「サイドチャネル攻撃」が広く知られています。本研究では、EMFPデータを収集し、サイドチャネル解析技術を応用することで、対象チップ固有の秘密鍵(ID情報)が取得できることを確認しました。

セキュリティ分野における攻撃者側の技術を、セーフティ分野に応用されたのですね。

本間先生の研究チームは、サイドチャネル解析のための豊富なツール群を有しており、さらに経年劣化に関する研究も並行して進めていたため、「劣化の進行度」と「IDの同定のしやすさ」の双方を学習データとして活用することができました。

たとえば、クロックの立ち上がりが鈍化して周波数特性に変化が生じた場合、IDの同定にどの程度の時間を要したのかといった情報を記録します。こうしたパターンを学習させることで、「IDの同定のしやすさ」から劣化の有無や進行度を推定するモデルを構築することが可能になります。

ただし現時点では、劣化の有無と、劣化が生じている場合における「進行度」の判定までにとどまっています。「○年分の経年劣化」といった具体的な年数を定量的に示す段階には至っていませんが、本研究は助成期間終了後も継続して発展させていく予定です。

本研究を通じて、半導体チップに劣化や故障を引き起こすストレス条件に関する多くの知見が得られた。これらをセキュリティ分野へフィードバックすることで、新たな研究の展開が期待される

先生方が今回開発された技術は、メーカーが有する既存技術とは異なる立ち位置にあるのでしょうか。

そうですね。既存技術としては、個々のデバイスが持つ物理的特徴を利用して固有のIDを生成し、個体認証を行うPUF(Physical Unclonable Function)があります。また、米国では国防高等研究計画局(DARPA)が、チップ内部に認証用の暗号回路を組み込むことで個体認証を実現する「SHIELDプロジェクト」を推進しています。

ただし、これらはいずれも「対応する暗号鍵を保持していること」が前提となっており、前回お話ししたように、基本的にはメーカー側が利用することを想定した技術です。また、経年劣化の評価という観点では、十分に研究が進んでいるとはいえません。

本研究の目的は、フェイクチップによるインシデントを未然に防ぎ、情報システムの安全性を確保することにあります。そのため、劣化していない正規品を使用することが理想ではありますが、仮に正規品でない場合であっても、劣化がなく安全に動作することが確認できるチップであれば、使用を検討する余地があると考えています。

今後はどのように研究を進めて、最終的にはどのような形のシステムになる予定でしょうか。

当初は研究用の高性能測定装置を用いていましたが、現在は入手しやすい機器でも計測できるよう、ツールチェーンの改良を含めたシステム全体の最適化を検討しています。イメージしているのは、小型プローブを電子機器の外側に当てるだけで、劣化の有無を判定できる装置です。

ただし、先ほど述べたように、経年劣化の研究はまだ途上にあります。どのようなストレス条件を与えれば、何年間使用した状態に相当する劣化となるのか。今後も実験とシミュレーションを繰り返しながら、経年劣化特性モデルの高度化と判定精度の向上を目指していきます。

この4年間、2カ月に一度、チーム全員が集まり全体ミーティングを実施してきた。進捗報告は1グループにつき30分と定めていたが、毎回時間を超過するほど活発な質問や議論が交わされた。大学の垣根を越えて緊密に連携し、着実に研究を推進することができたと感じている

本研究を通じて、半導体チップに劣化や故障を引き起こすストレス条件に関する多くの知見が得られた。これらをセキュリティ分野へフィードバックすることで、新たな研究の展開が期待される

本研究を通じて、半導体チップに劣化や故障を引き起こすストレス条件に関する多くの知見が得られた。これらをセキュリティ分野へフィードバックすることで、新たな研究の展開が期待される この4年間、2カ月に一度、チーム全員が集まり全体ミーティングを実施してきた。進捗報告は1グループにつき30分と定めていたが、毎回時間を超過するほど活発な質問や議論が交わされた。大学の垣根を越えて緊密に連携し、着実に研究を推進することができたと感じている

この4年間、2カ月に一度、チーム全員が集まり全体ミーティングを実施してきた。進捗報告は1グループにつき30分と定めていたが、毎回時間を超過するほど活発な質問や議論が交わされた。大学の垣根を越えて緊密に連携し、着実に研究を推進することができたと感じている