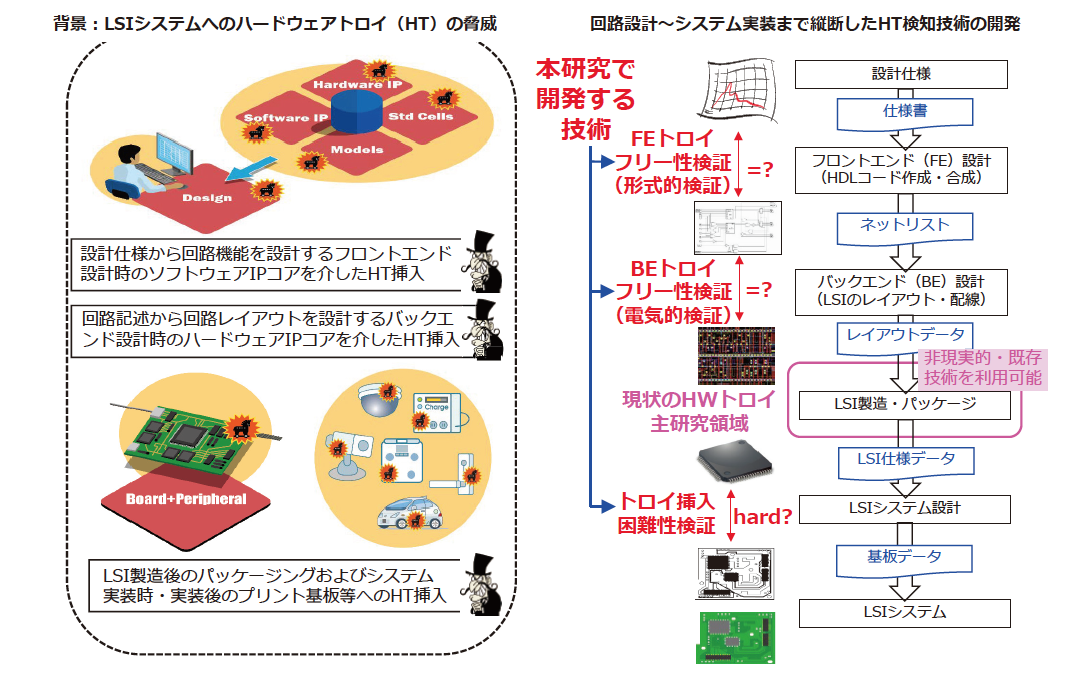

「トロイの木馬」をご存知でしょうか。アプリケーションなど害のないプログラムを装ってシステムに侵入・潜伏し、あるきっかけで外部に情報を流出する、情報を改ざんするなどの活動を開始するマルウェアです。ICチップ(集積回路)などに埋め込まれて作用するハードウェア版のトロイを、ハードウェアトロイ(HT)といいます。

HTはハードウェアの使用時に、利用者が想定していない任意のタイミングで動き出し、情報を外部に漏洩させたりします。以前、不正なデータアクセスを可能とする半導体があると米国で報道されたため、HTの脅威が広く知られるようになりました。

それ以前は、HTの社会的認知度は低いものでしたが、学会レベルでは問題視されていました。暗号回路にHTが挿入されれば機密情報の漏洩に繋がりますし、人工知能のICチップにHTが混入されれば、今後の情報社会においては大変な脅威となります。そうした背景から、私もHT混入を排除、抑止する技術開発に着手しました。

これまでは、LSI(大規模集積回路)の製造工場内に悪意ある人物が存在し、不正な改造を施すことが主に脅威と考えられていました。しかし、ある海外のLSI製造工場の責任者とお話しする機会があり、製造過程におけるHT混入の可能性について尋ねたところ、「可能性は極めて低い」という答えが返ってきました。現場の人間は正確な製造に集中しており、少しでも違う手順を加えることは難しく、また製造遅れが生じては信頼の喪失に繋がるため、HTを組み込むような余地はない、とのことでした。

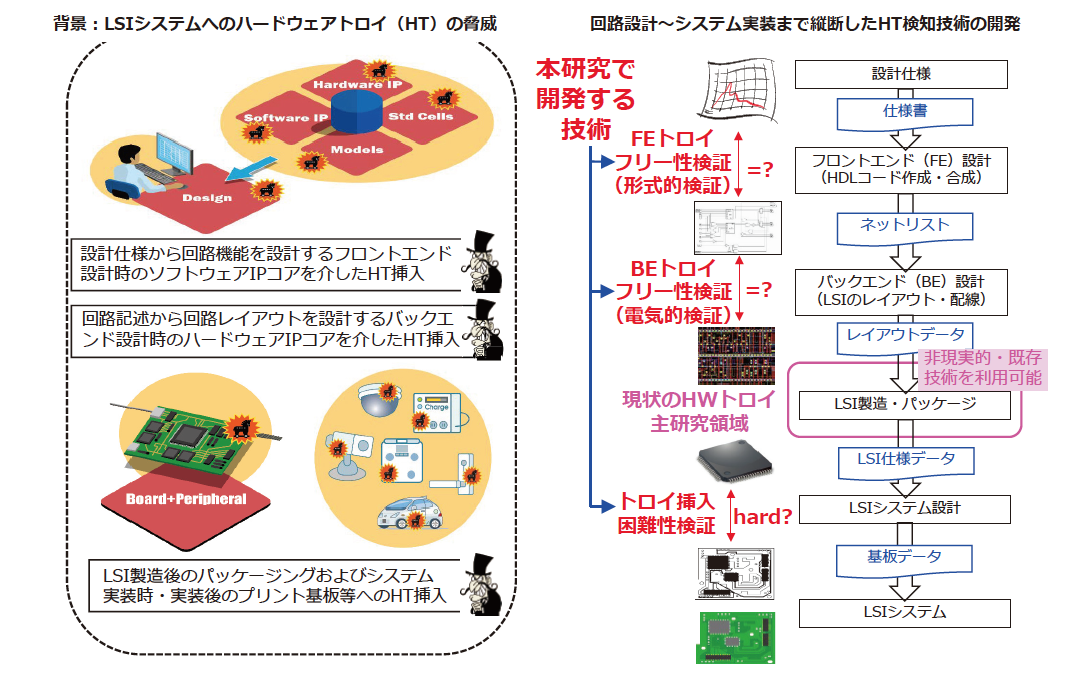

一方、LSIの設計時やボードへの実装前後におけるHT混入の脅威は、それまでほとんど議論されていませんでした。しかし、関係者との対話等を通じて、むしろ設計段階やシステム実装の段階でHTが混入する可能性のほうが高いことがわかってきたため、設計時と実装時でHTを検出する技術開発が必要だと考えたのです。

HTに関する研究は、主にLSI製造過程で挿入されるHTの検出を対象としており、製造前後の脅威を対象とした研究はほとんどなかった

そうです。まず設計仕様が決定され、その回路機能を実現するためのハードウェア記述言語(HDL)コードが設計されます。これをフロントエンド設計といいます。次に、HDLから回路レイアウトデータを設計するバックエンド設計があり、この設計図をもとにLSIが製造されます。最後に、製造したLSIのパッケージングとシステムへの実装が行われます。

本研究では、①フロントエンド設計時、②バックエンド設計時、③LSIパッケージングおよびシステム実装時の3段階に着目しました。

各段階で開発したHT検出技術を最終的に統合し、設計・仕様からLSIレイアウトデータまでのHTフリー化、HT挿入困難化を実現する設計・検証フレームワークの構築を目指す

各段階で開発したHT検出技術を最終的に統合し、設計・仕様からLSIレイアウトデータまでのHTフリー化、HT挿入困難化を実現する設計・検証フレームワークの構築を目指す

各段階で開発したHT検出技術を最終的に統合し、設計・仕様からLSIレイアウトデータまでのHTフリー化、HT挿入困難化を実現する設計・検証フレームワークの構築を目指す